Real Time Control Of Suspended Masses In Advanced VIRGO Laser Interferometer

Alberto Gennai for the VIRGO Collaboration

20th Real Time Conference 5-10 June 2016 Padova, Italy

Virgo is a laser interferometer designed to detect and observe gravitational waves. It is operated in Cascina, near Pisa on the site managed by the consortium European Gravitational Observatory (EGO), by an international collaboration of scientists from France, Italy, the Netherlands, Poland, and Hungary

**MOMVIK**

CINIS

INFN

Istituto Nazionale di Fisica Nucleare White the first of the second states and all the

INSTITUTE OF MATHEMATICS Polish Academy of Sciences

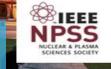

#### **VIRGO Interferometer**

#### **Gravitational Waves**

GW Signal is incredibly small: actual relative displacement is in the order of 6-8 x 10<sup>-18</sup> m (peak-to-peak)

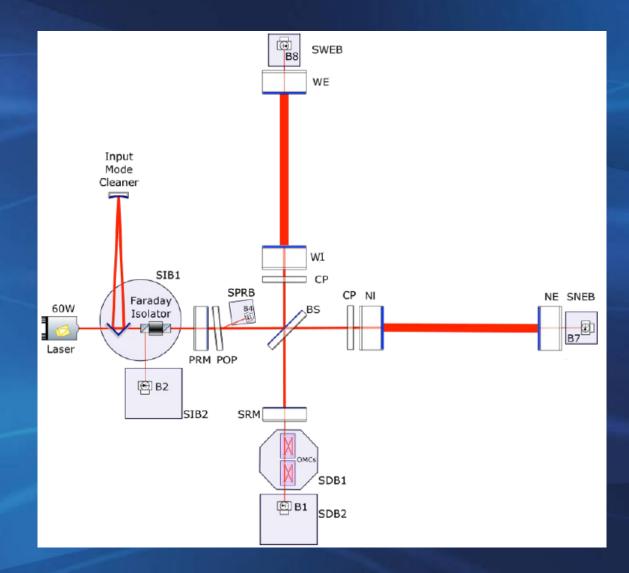

LIGO Hanford & Livingstone data: first direct detection

A. Gennai (INFN)

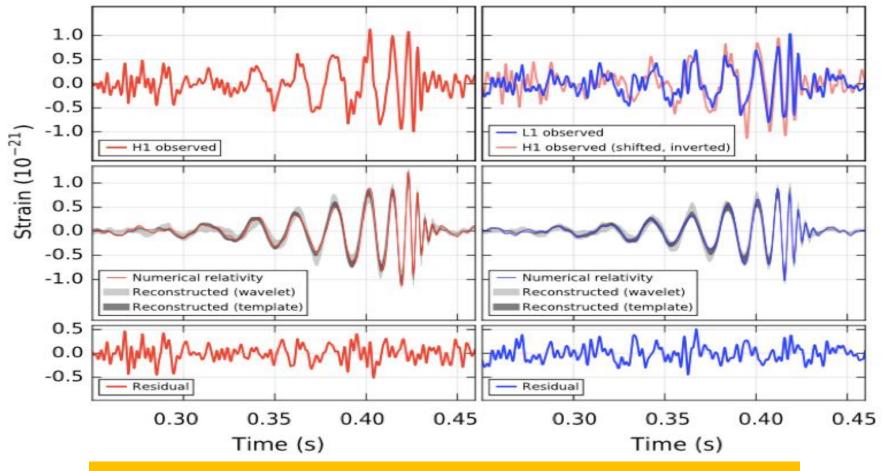

## Adv VIRGO Design Sensitivity

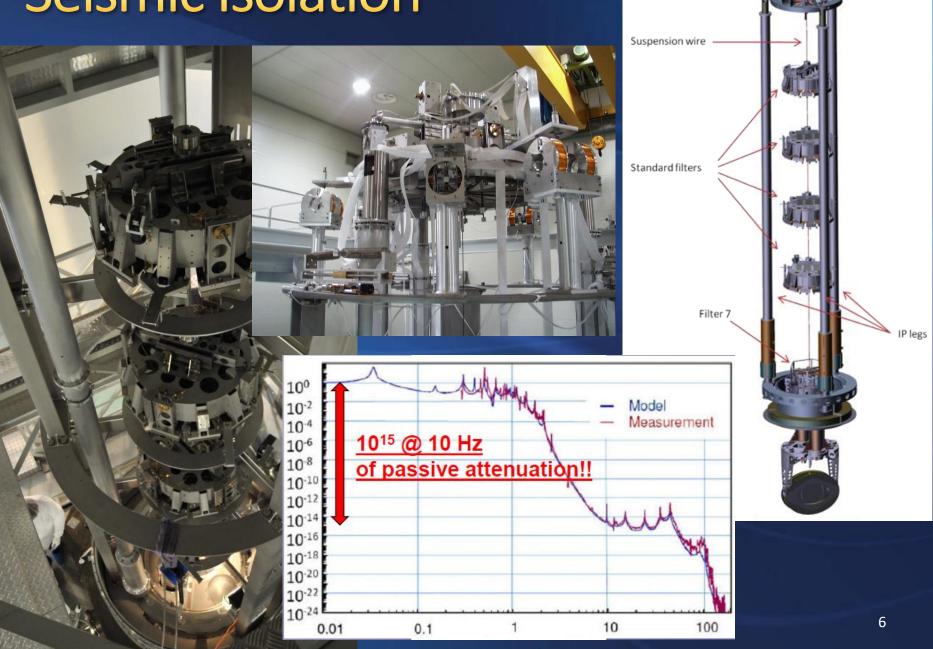

## **Seismic Isolation**

Filter 0

## Mirrors

## Control

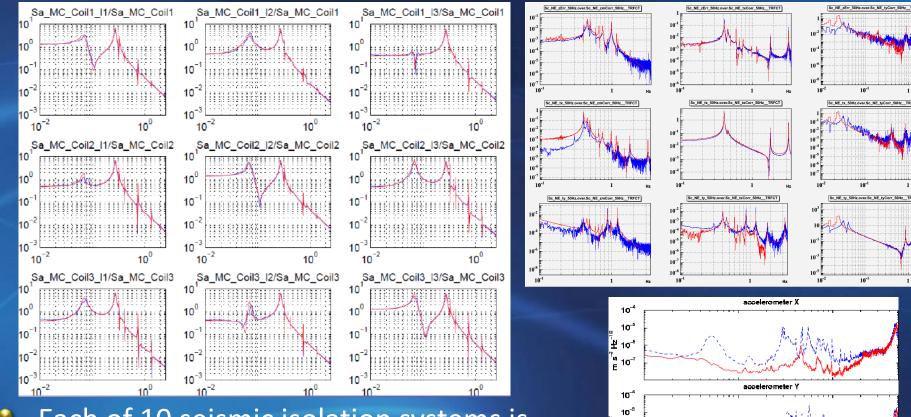

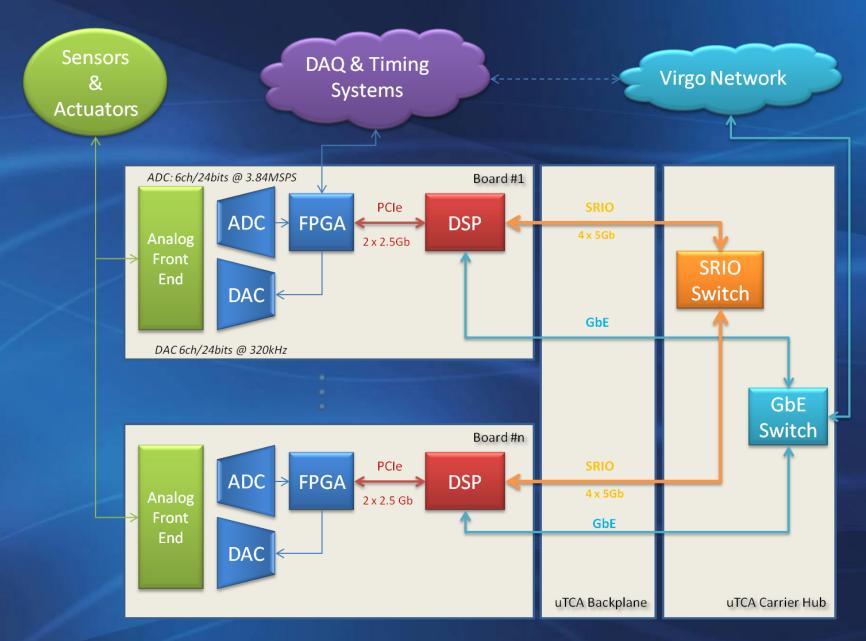

Each of 10 seismic isolation systems is equipped with inertial sensors (accelerometers), displacement sensors (LVDT and optical levers), stepping motors and magnet-coil actuators

#### **New Control System: Design Drivers**

- Move out of VME standard (limiting board-to-board communication bandwidth)

- Eliminate physical gap between analog-front end and data converters (in average we had more than 40 meters STP cabling, multiplied by about 100 signals for each of the 10 suspensions)

- Get out of rigid single sampling frequency operation (usually 10 kHz) and move on a more performing and flexible multi-rate system

- Further increase of locally available computation power to increase data quality analysis capabilities and properly assist control design and implementation mainly for the last stage of suspension and new payloads

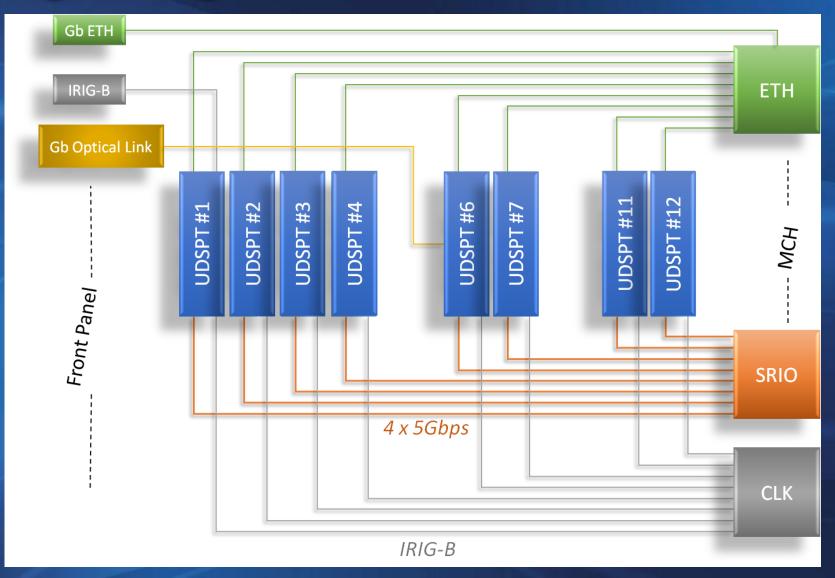

## **UDSPT Board**

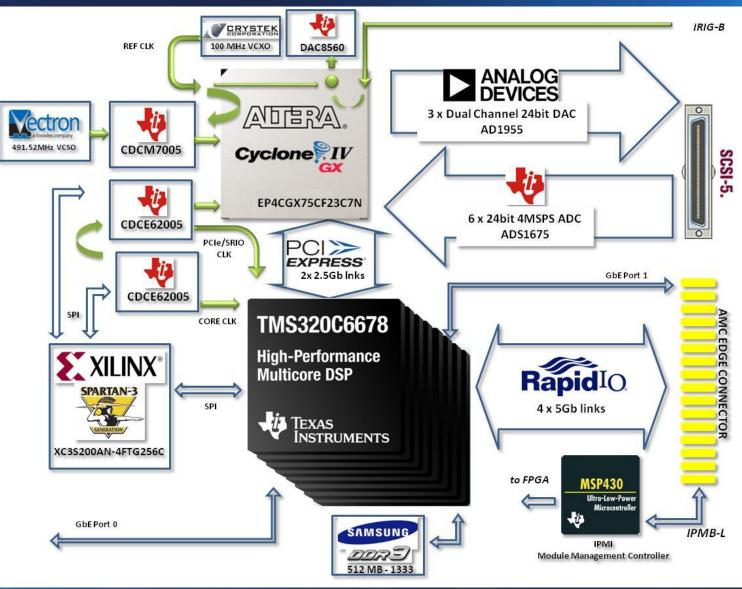

- Result of design effort is a high performance signal conditioning, signal conversion and processing platform that enables users to implement state of the art hard real time control system. Board can be operated in standalone mode or in cooperation with other boards.

- Form factor is a variation of a Double Compact Module PICMG<sup>®</sup> AMC.0 R2.0 AdvancedMC module (variation consists in a wider board than what specified for a Double Module)

- Key features of the UDSPT board include:

- Texas Instruments' multi-core DSP TMS320C6678

- 512 Mbytes of DDR3-1333 Memory

- Two Gigabit Ethernet ports supporting 10/100/1000 Mbps data-rate

- 170 pin B+ style AMC Interface containing SRIO and Gigabit Ethernet

- IRIG-B input

- Module Management Controller (MMC) for Intelligent Platform Management Interface (IPMI)

- Powered by DC power-brick adaptor (12V/3.0A) or AMC Carrier backplane

- Two on board FPGA: one Xilinx Spartan3 dedicated to processing unit and one Altera Cyclone IV interfacing data converters

- 6 x 24b 3.84 MHz ADC converters

- 3 x 24b 320 kHz DAC stereo converters (6 channels individually addressable)

- Converters sampling frequency DSP IRQs synchronous with IRIG-B signal

- Fully differential input channels and balanced output channels

#### **UDSPT Board**

## **UDSPT Board**

Board complexity (250 different parts, a total of 2500 components) was compensated by a modular design. Processing, data converters and front-end occupy pre-defined areas. Strong effort in interfaces design

## Performances

#### Digital I/O

Gb Ethernet Board- Rest of The World communication

- PCIe (2 x 2.5 Gbps) On-Board communication

- SRIO (4 x 5 Gbps) Board-to-board communication

#### DSP Software

- Operation up to 320 kHz sampling rate (3.125 usec interrupt request repetition cycle)

- Matrix(n,m)\*Vector(m,1) double precision multiplication requires 0.5\*nm+n+m nanoseconds:

- State space with 3 inputs, 3 outputs and 12 states requires less than 200 nsec

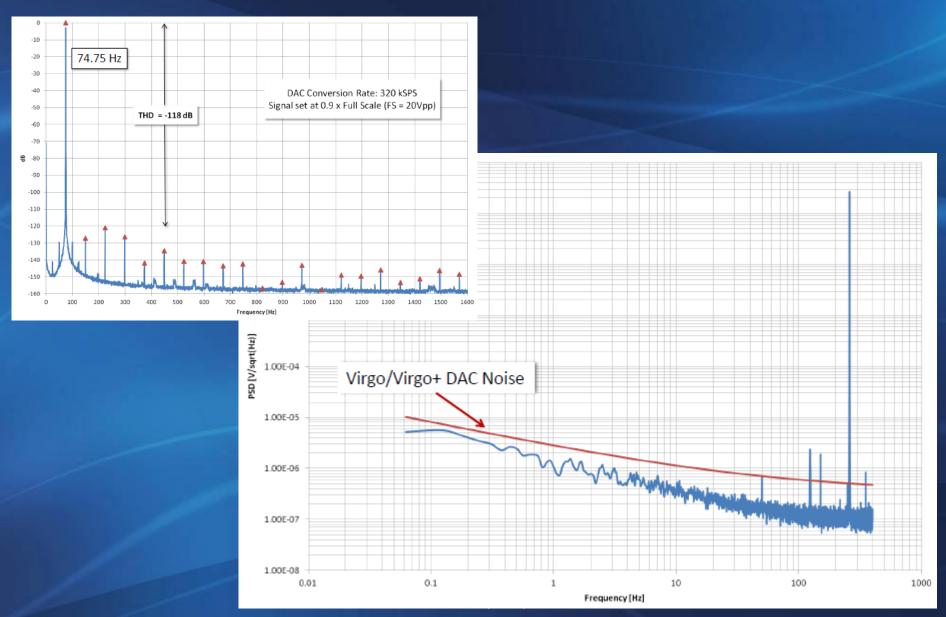

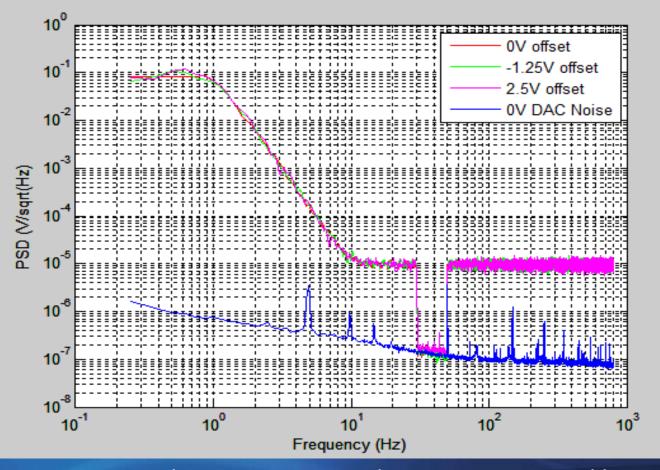

#### **DAC Perfomances**

#### **DAC Perfomances**

DAC output spectrum when converting a white spectrum signal low pass filtered (4 poles @ 1Hz + 4 zeroes @ 10 Hz) and stopband (30-50 Hz, Bessel 12th order,0.1dB ripple, -60 dB stopband). Signal amplitude was set to 0.6Vpp

A. Gennai (INFN)

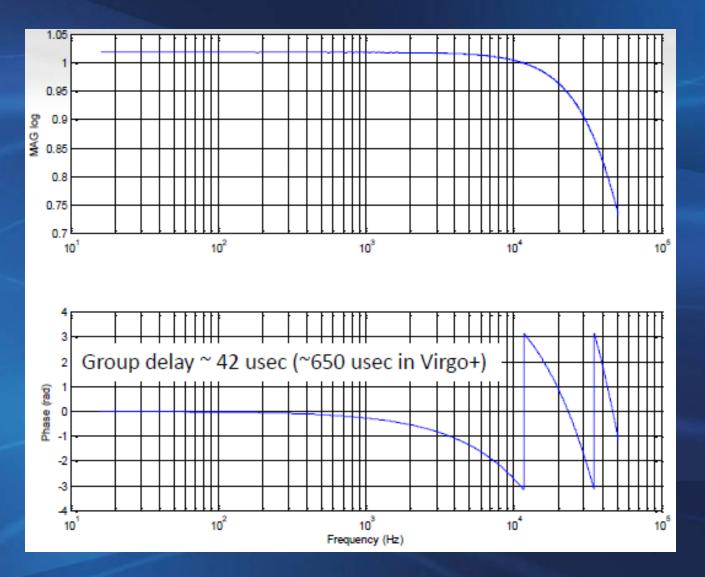

#### **DAC-DSP-ADS** Transfer Function

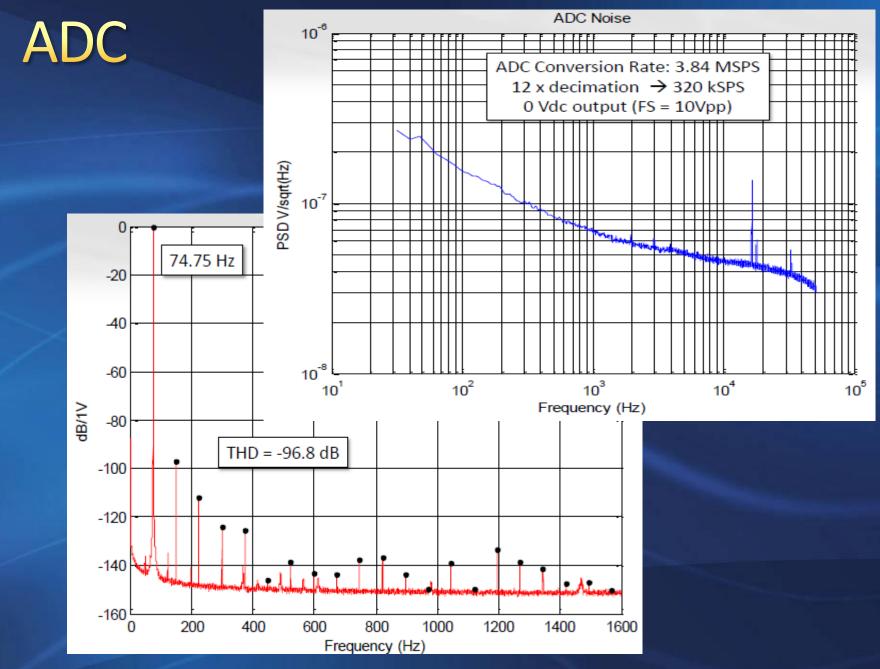

## Performances: ADC Noise & EMI

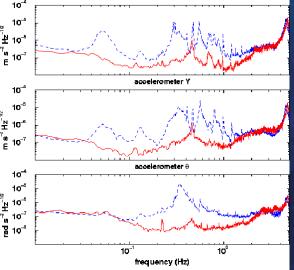

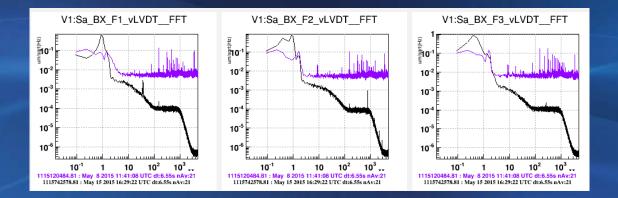

Performances tests on suspensions went beyond our expectation. Placing converters at front-end electronics level, together with introduction of digital demodulation, drastically improved noise immunity. Following picture shows improvement in vertical position sensors readout.

## Local Control Unit

In a single 6U x 19" crate we can concentrate 72 ADC + 72 DAC channels supported by 720 GFLOPs, 12 x 1 Gb Ethernet ports + 12 x 1 Gb Optical Link for digital IO and a total power consumption less than 500 Watts

# Deployment

Recently we completed the installation of 20 Local Contro Units for a total of 150 boards, 900 ADC channels and 900 DAC channels

## **Digital Signals Path**

## **Software Supervisor**

۲

For initial AdV, software shall support about 150 boards. At system startup each board loads boot code via tfpt from a dedicated boot server. This code is actually a sort of basic OS. In a second phase software supervisor (based on software toolkit Tango Controls) downloads in each processor the hard real-time code.

| SAT Supervisor (su cmpl3.virgo.infn.it)                                                                                              |            |                   |         |                                             |     |    |            |            |            |  |

|--------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|---------|---------------------------------------------|-----|----|------------|------------|------------|--|

|                                                                                                                                      |            |                   |         |                                             |     |    |            |            |            |  |

| File                                                                                                                                 |            |                   |         |                                             |     |    |            |            |            |  |

|                                                                                                                                      |            |                   |         |                                             |     |    |            |            |            |  |

| Sa_BS SC_BS EE Sa_IB SC_IB Sa_GA SC_GA Lab Sa_MC SC_MC Sa_NE SC_NE Sa_NI SC_NI Sa_OB Sa_PR SC_PR Sa_SR SC_SR Sa_WE SC_WE Sa_WI SC_WI |            |                   |         |                                             |     |    |            |            |            |  |

| 1                                                                                                                                    |            | dspserver/p42/80  | RUNNING | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_PSDi      | OFF | ON | Supervisor | Scope      | Properties |  |

| 2                                                                                                                                    | $\bigcirc$ |                   |         |                                             | OFF | ON | Supervisor | Scope      | Properties |  |

| 3                                                                                                                                    |            | dspserver/p42/108 | RUNNING | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_PSDm      | OFF | ON | Supervisor | Scope      | Properties |  |

| 4                                                                                                                                    |            | dspserver/p42/110 | RUNNING | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_PSDt      | OFF | ON | Supervisor | Scope      | Properties |  |

| 5                                                                                                                                    |            | dspserver/p42/84  | RUNNING | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_PSDf      | OFF | ON | Supervisor | Scope      | Properties |  |

| 6                                                                                                                                    |            | dspserver/p42/119 | RUNNING | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_Mir1      | OFF | ON | Supervisor | Scope      | Properties |  |

| 7                                                                                                                                    |            | dspserver/p42/115 | RUNNING | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_Mir2      | OFF | ON | Supervisor | Scope      | Properties |  |

| 8                                                                                                                                    |            | dspserver/p42/72  |         | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_Mar1      | OFF | ON | Supervisor | Scope      | Properties |  |

| 9                                                                                                                                    |            | dspserver/p42/85  | RUNNING | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_Mar2      | OFF | ON | Supervisor | Scope      | Properties |  |

| 10                                                                                                                                   |            | dspserver/p42/120 |         | /virgoDev/Sa/DSPCode_Adv/BS/F7/BS_F7_CD     | OFF | ON | Supervisor | Scope      | Properties |  |

| 11                                                                                                                                   |            | dspserver/p43/139 | RUNNING | /virgoDev/Sa/DSPCode_Adv/BS/LVDT/BS_F7_LVDT | OFF | ON | Supervisor | Scope      | Properties |  |

| 12                                                                                                                                   | $\bigcirc$ |                   |         |                                             | OFF | ON | Supervisor | Scope      | Properties |  |

| мс                                                                                                                                   | н 🔵        | mchserver/bs/2    | j       |                                             |     |    | Rebo       | ot chassis | Properties |  |

| PDL                                                                                                                                  | <b>ا</b>   | pduserver/bs/1    | #8      |                                             |     |    | OF         | F ON       | Properties |  |

|                                                                                                                                      |            |                   |         |                                             |     |    |            |            |            |  |

**T**ANG

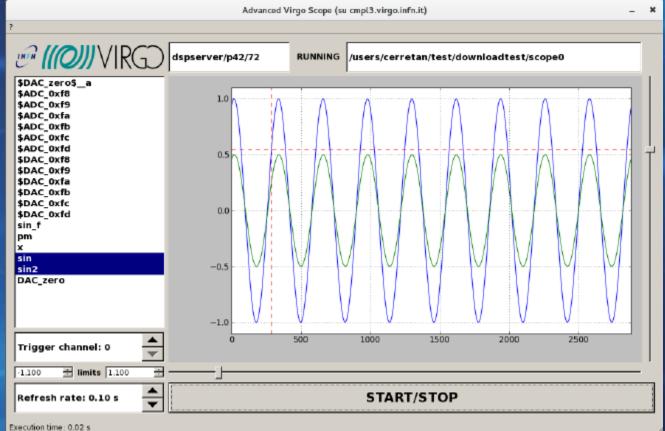

# **Real Time Scope**

A nice tool for system debugging is a realtime scope that can access any single variable declared into the source code. Work is in progress to provide real-time fft and few more functionalities

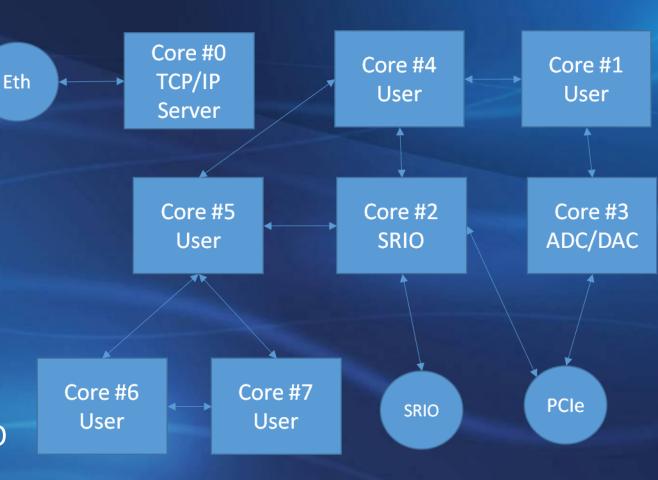

# **DSP** Cores

Each DSP core, excluding C#0, runs a single task activated at a fixed frequency lower or equal to 320 kHz

۵

- Communication is memory mapped using a 2 stages FIFO (ping-pong table)

- 5 out of the 8 cores available are user programmable

## DSP Code

| 1 #include <asm header.net=""> 2 NETLIST { 3 4 START { 5 SAMPLING FREQ = 10000; 6 OVER SAMPLING = 1;</asm> | 1 .tab 6<br>2 DAQ_header1 .equ 00055045h<br>3 DAQ_header2 .equ 00055046h<br>4 DMA7_chain .equ 000517e8h<br>5 tolm_in_dpm_buffer .equ 14831a00h<br>6 tolm_in_ser_buffer .equ 14831c00h                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>4 START {<br>5 SAMPLING_FREQ = 10000;                                                                 | 3 DAQ_header2 .equ 00055046h<br>4 DMA7_chain .equ 00051788h<br>5 tolm_in_dpm_buffer .equ 14831a00h<br>6 tolm_in_ser_buffer .equ 14831c00h                                                                                                                                                                                                                        |

| 5 SAMPLING_FREQ = 10000;                                                                                   | 4 DMA7 chain .equ 000517e8h<br>5 tolm_in_dpm_buffer .equ 14831a00h<br>6 tolm_in_ser_buffer .equ 14831c00h                                                                                                                                                                                                                                                        |

| 5 SAMPLING_FREQ = 10000;                                                                                   | 4 DMA7_chain .equ 000517e8h<br>5 tolm_in_dpm_buffer .equ 14831a00h<br>6 tolm_in_ser_buffer .equ 14831c00h                                                                                                                                                                                                                                                        |

|                                                                                                            | 5 tolm_in_dpm_buffer .equ 14831a00h<br>6 tolm_in_ser_buffer .equ 14831c00h                                                                                                                                                                                                                                                                                       |

|                                                                                                            | 6 tolm_in_ser_buffer .equ 14831c00h                                                                                                                                                                                                                                                                                                                              |

| 6 OVER SAMPLING = 1;                                                                                       |                                                                                                                                                                                                                                                                                                                                                                  |

| 7 USE $\overline{ADC} = 1;$                                                                                | 7 tolm in glb buffer .equ 14831800h                                                                                                                                                                                                                                                                                                                              |

| 8 DOWN SAMPLING = 1;                                                                                       | 8 tolm1 out buffer .equ 00058300h                                                                                                                                                                                                                                                                                                                                |

| 9 W COEFF = internal;                                                                                      | 9 tolm2 out buffer .equ 00058700h                                                                                                                                                                                                                                                                                                                                |

| 10 SOURCE = parent;                                                                                        | 10 Guard1 to Core0 .equ 1087f000h                                                                                                                                                                                                                                                                                                                                |

| 11 DOL ADDR = f94c0000;                                                                                    |                                                                                                                                                                                                                                                                                                                                                                  |

| 12 GRD ADDR = Guard4 to Core0;                                                                             | 11 Guard4_to_Core0 .equ 1483c400h                                                                                                                                                                                                                                                                                                                                |

| 13 DICT NAME = SC NI;                                                                                      | 12 .sect .textasm ; program section                                                                                                                                                                                                                                                                                                                              |

| 14 KEEP VALUES = no;                                                                                       | 13                                                                                                                                                                                                                                                                                                                                                               |

| 15 DECAY TIME = 0x00000000;                                                                                | 14 SP .set b15                                                                                                                                                                                                                                                                                                                                                   |

| 16                                                                                                         | 15                                                                                                                                                                                                                                                                                                                                                               |

| 17 TOLM OUT N = 1;                                                                                         | 16 .global dsp_irq                                                                                                                                                                                                                                                                                                                                               |

| 18 TOLM OUT = {                                                                                            | 17 .global i_list                                                                                                                                                                                                                                                                                                                                                |

| 19 {                                                                                                       | 18 .global c_list                                                                                                                                                                                                                                                                                                                                                |

| 20 PAGE = 0x00000000;                                                                                      | 19 .global w_list                                                                                                                                                                                                                                                                                                                                                |

| 21 NAME = PRB;                                                                                             | 20 .global noise_table                                                                                                                                                                                                                                                                                                                                           |

| 22 ROUTING = 0xf94c0000;                                                                                   | 21 .global cosine_table                                                                                                                                                                                                                                                                                                                                          |

| 23 TOLM = TOLM1;                                                                                           | 22 .global input list                                                                                                                                                                                                                                                                                                                                            |

| 24 }                                                                                                       | 23 .global output list                                                                                                                                                                                                                                                                                                                                           |

| 25 )                                                                                                       | 24 .global Guard4 to Core0                                                                                                                                                                                                                                                                                                                                       |

| 26 }                                                                                                       | 25 dsp_irq:                                                                                                                                                                                                                                                                                                                                                      |

| 27                                                                                                         | 26 .asmfunc                                                                                                                                                                                                                                                                                                                                                      |

| 28 ASM START {}                                                                                            | 27                                                                                                                                                                                                                                                                                                                                                               |

| 29                                                                                                         | 28 mvc CSR, B2 ; save old interrupt status                                                                                                                                                                                                                                                                                                                       |

| 30 DAC SETUP {                                                                                             | 29    add -8,SP,SP                                                                                                                                                                                                                                                                                                                                               |

| 31  NDAC = 6;                                                                                              | 30 DINT ; disable interrupts                                                                                                                                                                                                                                                                                                                                     |

| 32 OUT = (\$DAC 0xf8, \$DAC 0xf9, \$DAC 0xfa, \$DAC 0xfb,                                                  | 31 stdw A11:A10, *SP[1] ; a10 = call in                                                                                                                                                                                                                                                                                                                          |

| 33 \$DAC 0xfc, \$DAC 0xfd);                                                                                | 32 stdw A13:A12, *SP[1] ; a12 = tolm out address                                                                                                                                                                                                                                                                                                                 |

| 34                                                                                                         | 33 stdw A15:A14, *SP[1]                                                                                                                                                                                                                                                                                                                                          |

| 35                                                                                                         | 34 stdw B11:B10, *SP[1] ; b10 = call out                                                                                                                                                                                                                                                                                                                         |

| 36 ASM CONTINUE {}                                                                                         | 35 stdw B13:B12, *SP[1] ; b12 = tolm in address                                                                                                                                                                                                                                                                                                                  |

| 37                                                                                                         | 36         stdw         B13.B12, "SE[1]         , b12 - tolm_ln_address           36         stdw         B9:B8, *SE[1]         ; b8 = From Slot buffer address                                                                                                                                                                                                  |

| 38 CALL {                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                  |

| 43 OUT = (lvdt1, lvdt2, lvdt3, vlvdt1, vlvdt2, vlvdt3, ratio 11, ratio 12,                                 | 41 stw B4, *SP[1] ; save DAC address                                                                                                                                                                                                                                                                                                                             |

| 44 (ratio 13);                                                                                             |                                                                                                                                                                                                                                                                                                                                                                  |

| <pre>39 NAME = NI_F7_LVDT_Demod.hrd;<br/>40</pre>                                                          | 37         stdw         B3:B2, *SP[1]           38         stw         A8, *SP[1]         ; save To_Slot buffer address           39         stw         B6, *SP[1]         ; save signals buffer address           40         stw         A6, *SP[1]         ; save probe buffer address           41         stw         B4, *SP[1]         ; save DAC address |

From a source code written in a simple objectoriented language we generate asm code for the cross-compiler that produces DSP binary code

## Conclusions

A new system to control suspensions and mirrors was developed and installation is now completed.

- Extensive use of supervising software, mysql databases and third parties tools will simplify operation and maintenance

- Simple user interfaces allow writing real-time DSP code without having specific training